# Simple Circuit Extensions for XOR in PTIME

2 **Anonymous author**

3 Anonymous affiliation

4 **Anonymous author**

5 Anonymous affiliation

6 **Anonymous author**

7 Anonymous affiliation

## 8 — Abstract —

---

9 The Minimum Circuit Size Problem for Partial Functions (MCSP\*) is hard assuming the Exponential

10 Time Hypothesis (ETH) (Ilango, 2020). This breakthrough hardness result leveraged a characteriza-

11 tion of the optimal  $\{\wedge, \vee, \neg\}$  circuits for  $n$ -bit OR ( $OR_n$ ) and a reduction from the partial

12  $f$ -Simple Extension Problem where  $f = OR_n$ . It remains open to extend that reduction to show

13 ETH-hardness of total MCSP. However, Ilango observed that the total  $f$ -Simple Extension Problem

14 is easy whenever  $f$  is computed by read-once formulas (like  $OR_n$ ). Therefore, extending Ilango’s

15 proof to total MCSP would require one to replace  $OR_n$  with a slightly more complex but similarly

16 well-understood Boolean function.

17 This work shows that the  $f$ -Simple Extension problem remains easy when  $f$  is the next natural

18 candidate:  $XOR_n$ . We first develop a fixed-parameter tractable algorithm for the  $f$ -Simple Extension

19 Problem that is efficient whenever the optimal circuits for  $f$  are (1) linear in size, (2) polynomially

20 “few” and efficiently enumerable in the truth-table size (up to isomorphism and permutation of

21 inputs), and (3) all have constant bounded fan-out.  $XOR_n$  satisfies all three of these conditions.

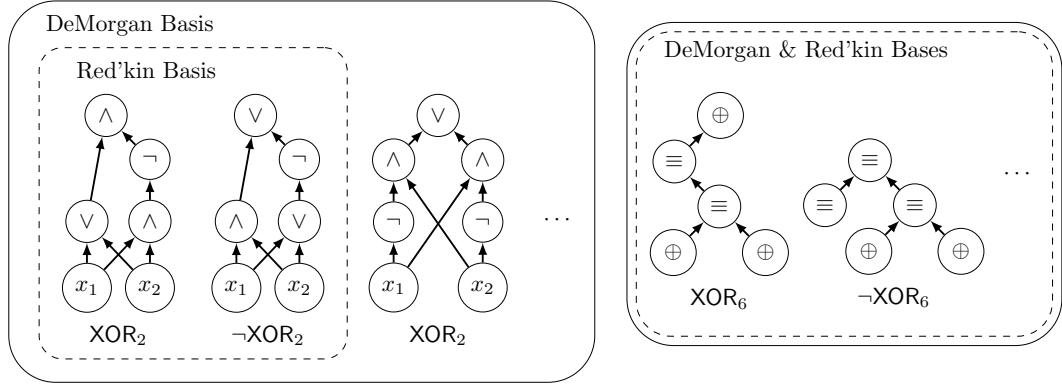

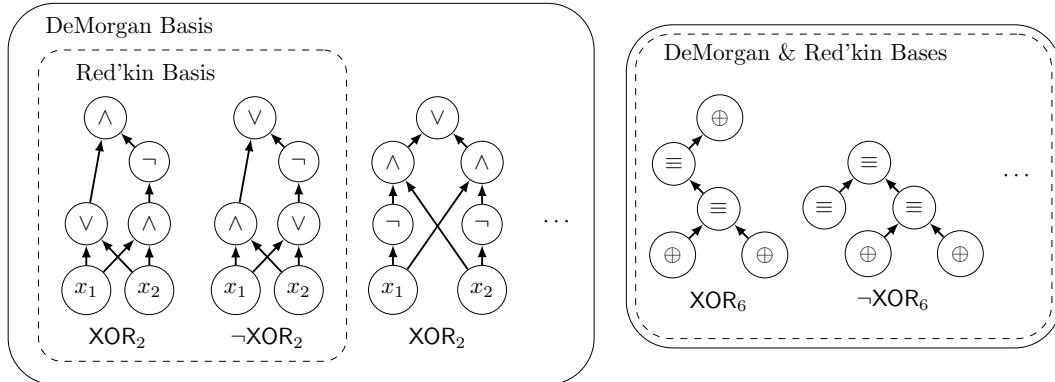

22 When  $\neg$  gates count towards circuit size, optimal  $XOR_n$  circuits are binary trees of  $n - 1$  subcircuits

23 computing  $(\neg)XOR_2$  (Kombarov, 2011). We extend this characterization when  $\neg$  gates do not

24 contribute the circuit size. Thus, the  $XOR$ -Simple Extension Problem is in polynomial time under

25 both measures of circuit complexity.

26 We conclude by discussing conjectures about the complexity of the  $f$ -Simple Extension problem

27 for each explicit function  $f$  with general circuit lower bounds over the DeMorgan basis. Examining the

28 conditions under which our Simple Extension Solver is efficient, we argue that *multiplexer* functions

29 ( $MUX$ ) are the most promising candidate for ETH-hardness of a Simple Extension Problem, towards

30 proving ETH-hardness of total MCSP.

31 **2012 ACM Subject Classification** Theory of computation → Circuit complexity; Theory of compu-

32 tation → Fixed parameter tractability

33 **Keywords and phrases** Minimum Circuit Size Problem, Circuit Lower Bounds, Exponential Time

34 Hypothesis

35 **Digital Object Identifier** 10.4230/LIPIcs.CVIT.2016.23

© Anonymous author(s);

licensed under Creative Commons License CC-BY 4.0

42nd Conference on Very Important Topics (CVIT 2016).

Editors: John Q. Open and Joan R. Access; Article No. 23; pp. 23:1–23:40

Leibniz International Proceedings in Informatics

LIPICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

36 **1** Introduction

37 Circuits model the computation of Boolean functions on fixed input lengths by acyclic wires

38 between atomic processing units — logical “gates.” To measure the circuit complexity of

39 a function  $f$ , we first fix a set of gates  $\mathcal{B}$  — called a *basis*. This work studies circuits over

40 the following basis: fan-in 2 AND, fan-in 2 OR, and fan-in 1 NOT gates. We consider two

41 complexity size measures  $\mu_{\mathcal{D}}$  and  $\mu_{\mathcal{R}}$ , which count *only* the binary gates and the *total* number

42 of gates in a circuit respectively. We will refer to  $\mathcal{B}$  equipped with these two complexity

43 measures as  $\mathcal{D}$ , the DeMorgan basis, and  $\mathcal{R}$ , the Red’kin basis respectively<sup>1</sup>.

44 Basic questions about these models have been open for decades; we cannot even rule

45 out the possibility that every problem in NP is decided by a sequence of linear-size circuits

46 (see page 564 of [22]). Despite this, the ongoing search for circuit complexity lower bounds

47 has fostered rich and surprising connections between cryptography, learning theory, and

48 algorithm design [16, 12, 37, 6, 36, 17]. The *Minimum Circuit Size Problem* (MCSP, [23])

49 appears in all of these areas, asking:

50 Given an  $n$ -input Boolean function  $f$  as a  $2^n$ -bit truth table, what is the minimum  $s$

51 such that a circuit of size  $s$  computes  $f$  ?

52 The **existential** question — do functions that require “many” gates exist? — was solved

53 in 1949: Shannon proved that almost all Boolean functions require circuits of near-trivial<sup>2</sup>

54 size  $\Omega(\frac{2^n}{n})$  by a simple counting argument [40]. The current best answer to the **explicit**

55 question in the DeMorgan basis — is such a hard function in NP? — is a circuit lower bound

56 of  $5n - o(n)$ , proved via *gate elimination* [21]. This is far from the popular conjecture that

57 NP-complete problems require super-polynomial circuit size.

58 The **algorithmic** question — is MCSP NP-hard? — remains open after nearly fifty years

59 [41], even under strong complexity assumptions such as the Exponential Time Hypothesis

60 (ETH). But, many natural variants of MCSP have been proven NP-hard unconditionally.

61 For instance, DNF-MCSP [31], MCSP for OR-AND-MOD Circuits [15], and MCSP for multi-

62 output functions [20] are now known to be NP-hard. Furthermore, MCSP for partial functions

63 (MCSP\*) [18] is hard under the Exponential Time Hypothesis (ETH), later extended to

64 unconditional NP-hardness under randomized reductions [14].

65 Our work studies the feasibility of generalizing Ilango’s technique for ETH-hardness of

66 MCSP\* to total MCSP. In particular, underlying Ilango’s proof is a related decision problem

67 about circuit complexity of Boolean *simple extensions* which we call the  $f$ -Simple Extension

68 Problem ( $f$ -SEP).

69 ▶ **Definition (Simple Extension).** Let  $f$  be a Boolean function that depends on all of its  $n$

70 variables. A simple extension of  $f$  is either  $f$  itself or a function  $g$  on  $n + m$  variables

71 satisfying:

- 72 1.  $g$  depends on all of its inputs.

- 73 2.  $CC(g)$  — the circuit-size complexity of  $g$  — is  $CC(f) + m$ .

- 74 3. There exists a setting  $k \in \{0, 1\}^m$ , a key, such that for all  $x \in \{0, 1\}^n$ ,  $g(x, k) = f(x)$ .

- 75 We define the  $f$ -Simple Extension decision problem for total functions below.<sup>3</sup>

<sup>1</sup> We will specify a basis if a statement pertains to *only* that basis. If the basis is not specified, then the statement applies to both  $\mathcal{D}$  and  $\mathcal{R}$ .

<sup>2</sup> From using a lookup table.

<sup>3</sup> For partial function  $f$ -Simple Extension ( $f$ -SEP\*),  $g$  is a *partial* function and we must determine whether any completion of  $g$  is a simple extension of  $f$ .

76 **► Problem** (The  $f$ -Simple Extension Problem). Let  $f$  be a sequence of Boolean functions

77  $\{f_n\}_{n \in \mathbb{N}}$  such that each  $f_n$  depends on all of its  $n$  inputs. The  $f$ -Simple Extension Problem

78 is defined as follows: Given  $n \in \mathbb{N}$  and  $tt(g)$ —the truth table of a binary function  $g$ —decide

79 whether  $g$  is a simple extension of  $f_n$ .

80 For a fixed  $f$  whose truth table can be efficiently computed and whose exact circuit

81 complexity is known,  $f$ -SEP reduces to a single call to an MCSP oracle, because checking

82 whether  $g$  is a non-degenerate extension of  $f$  can be done in polynomial time via brute force

83 (given the truth table of  $g$ ). This observation gives rise to an MCSP-hardness proof framework:

84 if one can identify an explicit function  $f$  for which deciding the  $f$ -Simple Extension Problem

85 is hard, then MCSP is also hard.

86 This framework was implicitly used in Ilango's hardness proof for MCSP\* [18], i.e. reducing

87 an ETH-hard problem to deciding whether a partial function is a simple extension of  $f = \text{OR}$ .

88 We make this observation explicit in Section 2. Now, a natural question arises: can one

89 extend this idea to total MCSP and prove  $\text{MCSP} \notin \text{P}$  assuming ETH? Ilango suggested that

90 “the most promising approach is to skip MCSP\* entirely and extend our techniques to

91 apply to MCSP directly.” - Rahul Ilango, SIAM J. of Computing, 2022

92 However, optimal circuits for  $\text{OR}$  are so well-structured that deciding whether a *total*

93 function is a simple extension of it is actually easy (see the discussion in Section 1.2.2 in

94 [18]). Minimal  $\text{OR}$  circuits are *read-once formulas*: each of the input is read exactly once and

95 each internal gate has fan-out 1. Simple extensions of it will also be computed by read-once

96 formulas, and deciding whether a given Boolean function has a read-once formula is *easy*

97 [2, 13]. Therefore,

98 “the missing component in extending our results to MCSP is finding some function  $f$

99 whose optimal circuits we can characterize but are also sufficiently complex.” - Rahul

100 Ilango, SIAM J. of Computing, 2022

101 Could simply replacing  $\text{OR}$  with some read-many  $f$  — perhaps  $\text{XOR}$ , which enjoys tight

102 bounds and a full characterization — allow Ilango's technique to prove MCSP is ETH-hard?

103 For  $\text{XOR}$ , we show the answer is a resounding **no**. For other potential functions, the answer

104 is more ambiguous. We will discuss prospects for alternative hard functions in Section 1.3.

## 105 1.1 Our Results and Contributions

106 We narrow the field of candidate functions for such a hardness proof by developing a fixed-

107 parameter tractable algorithm for the  $f$ -Simple Extension problem (Section D.4). Such an

108 algorithm is surprising, because  $f$ -Simple Extension is a meta-complexity problem about

109 *general circuits* and our algorithm works in regimes where we *know* explicit circuit lower

110 bounds. Often, the combinatorial facts used in lower bounds imply a hardness result for

111 the appropriately-restricted meta-complexity problem (e.g., DNF-MCSP)! Nonetheless, we

112 obtain:

113 **► Main Result.** The  $f$ -Simple Extension Problem is in  $\text{P}$  whenever

- 114 1.  $CC(f)$  — the circuit-size complexity of  $f$  — is linear,

- 115 2. the maximum fan-out over all optimal circuits for  $f$  is constant, and

- 116 3. the optimal<sup>4</sup> circuits for  $f$ , up to isomorphism and permutation of its  $n$  inputs, are

117 efficiently enumerable and polynomial few with respect to the length of its truth table:  $2^n$ .

---

<sup>4</sup> In  $\mathcal{D}$ , we require a circuit to be *normalized* for it to be optimal. In particular, it cannot contain any double-negations. This prevents every function from having an infinite number of optimal circuits.

## 23:4 Simple Circuit Extensions for XOR in PTIME

118 To apply our main result and discount a particular  $f$ , we require an exact specification of

119 its optimal circuits. The next natural candidate — XOR, a simple function whose circuits

120 are neither read-once nor monotone — has been well studied. Beyond enjoying exact size

121 bounds [39, 35], XOR is one of the few functions whose structure has been studied; it is

122 known that, in  $\mathcal{R}$ , all optimal  $\text{XOR}_n$  circuits are binary trees of  $n - 1$   $\text{XOR}_2$  sub-blocks [25].

123 We extend this structural analysis to  $\mathcal{D}$  in Section E, obtaining

124 ▶ **Main Lemma** ([25], Theorem 37). *Optimal  $\text{XOR}_n$  circuits consist of  $(n - 1)$   $(\neg)\text{XOR}_2$

125 sub-circuits.*

126 Each  $\text{XOR}_n$  circuit can therefore be characterized using binary trees with  $n$  leaves, of

127 which there are  $C_{n-1} = O(2^n)$ , where  $C_n$  is the  $n^{\text{th}}$  Catalan number [42]. As there are a

128 finite number of optimal normalized  $(\neg)\text{XOR}_2$  circuits, combining this characterization and

129 our main result to immediately yields

130 ▶ **Main Corollary.** *The XOR-Simple Extension Problem is in P.*

131 Applying Ilango’s technique successfully will itself require a deeper study of circuit

132 minimization. This is not merely because any hardness proof needs to bypass our algorithm;

133 knowledge of circuit lower-bounds and optimal constructions for the base function is intrinsic

134 to the reduction itself. We make this connection explicit in Section 2, identifying that

135 ▶ **Main Observation.**  *$f$ -SEP\* is ETH-hard under Levin reductions.*

136 Lastly, in Section 1.3, we inspect each explicit function  $f$  that enjoys DeMorgan circuit

137 lower bounds and argue how plausible it is that the optimal set of  $f$  circuits avoids our Main

138 Result — a *roadmap* towards ETH-hardness of total MCSP via  $f$ -SEP.

## 139 1.2 Related Work

140 **(Non-)hardness of MCSP Variants.** Hirahara showed that *Partial* MCSP is unconditionally

141 NP-hard under *randomized reductions* [14]. Extending his breakthrough result is another

142 approach towards hardness of total MCSP. Though promising, this also faces challenges: under

143 believable cryptographic conjectures (indistinguishability obfuscation and subexponentially-

144 secure one-way functions), GapMCSP is not NP-complete under randomized Levin-reductions

145 [32]. Such reductions appear to suffice for Hirahara’s proofs, so one may need new ideas to

146 obtain NP-hardness of total MCSP via his approach.

147 We bypass the issue by working towards hardness of total MCSP under ETH — a stronger

148 assumption than  $P \neq NP$ . Even so, ETH-hardness of total MCSP remains a major open

149 problem, and there are no known barriers to extending Ilango’s approach in this setting. The

150 reader can decide for themselves if our algorithm constitutes such a barrier or not.

151 **Optimal Circuit Structures.** Knowing the lower-bounds of some explicit Boolean functions

152  $f$ , a natural question to ask is: *What about the structure of every optimal circuit computing*

153  $f$ ? For some functions and bases, this is easy to answer: minimal Red’kin circuits for  $\text{OR}_n$  are

154 binary trees of  $\vee$  gates. For even slightly more complex functions, structural characterization

155 seems to require intricate and exhaustive case analysis. Some of the earliest work on this

156 question include [38] and [5] which investigated when optimal circuits for certain 2-output

157 Boolean functions must compute each output independently. More recently, Kombarov

158 extended the characterization of XOR circuits to other complete bases when NOT-gates are

159 counted [26].

160 **1.3 Discussion and Future Directions**

161 **A Remark on Bases.** Both  $\mathcal{R}$  and  $\mathcal{D}$  are compatible with Ilango’s proof of ETH-hardness

162 of MCSP\*. That proof relied on functions whose optimal  $\{\wedge, \vee, \neg\}$ -circuits are read-once

163 monotone formulas. There it was irrelevant whether  $\neg$  gates contribute to size: those circuits

164 simply did not contain negations. However, when we move to more complex functions like

165 XOR, negations *must* appear in the optimal circuits and as such, we must decide how to

166 treat them.

167 In the search for non-linear circuit lower bounds, the choice between  $\mu_R$  and  $\mu_D$  is largely

168 irrelevant: the two complexity measures the same up to a small constant factor. However, as

169 we discuss in Section 2, Ilango’s technique requires knowledge of the *structure* of optimal

170 circuits. In this setting, there is not necessarily as strong connection between the two bases.

171 By extending Kombarov’s characterization of XOR circuits in  $\mathcal{R}$  to  $\mathcal{D}$  in Section E, we show

172 for that *particular* function, optimal circuits are structurally similar in both bases. But, for

173 other functions, this may well not be the case. It seems likely that negations could enable

174 a function’s optimal circuits to greatly vary under the two complexity measures. Indeed,

175 negations can greatly increase a problems complexity: [4] showed that a Boolean function

176 learning problem became difficult only once the number of  $\neg$  gates exceeded a small threshold.

177 By considering both bases in this work, we limit how negations impact the complexity of

178  $f$ -SEP. We show that they do not greatly increase the complexity of the simple extensions

179 themselves: in Section C, we find that simple extensions under both complexity measures

180 are highly structured. If a future hardness reduction relies on negations, their role will be in

181 increasing the structural complexity of the underlying base function, either by increasing the

182 number of distinct optimal circuits, or by enabling non-constant fan-out in a base circuit.

183 **A Roadmap for ETH-Hardness Proofs via Simple Extensions** To prove  $f$ -SEP is ETH-hard

184 we will need a Boolean function whose optimal circuits are more complex and/or varied

185 than XOR. Specifically, these circuits must either (1) be superlinear in size, (2) require

186 non-constant fanout, or (3) be sufficiently numerous. Superlinear bounds seem beyond

187 current techniques—the most fruitful of which, gate elimination, seems unlikely to be able to

188 prove lower bounds above even  $11n$  for wide classes of functions [11]. As such, it seems more

189 sensible to identify Boolean functions which violate the latter conditions. However, structural

190 characterization of the optimal circuits is also hard, and seems to require very tight circuit

191 bounds. Indeed, our DeMorgan basis characterization of XOR repeatedly exploited Schnorr’s

192 *exact*  $3(n - 1)$  bound for  $\text{XOR}_n$  [39]. Regardless, this greatly narrows the prospective class of

193 functions from the original specification: “more complex than read-once formulas.” However,

194 the known explicit functions with tight DeMorgan bounds that may violate these conditions

195 are few and far between. In Table 1<sup>5</sup>, we summarize these explicit functions and assess how

196 suitable they are for ETH-hardness of  $f$ -Simple Extension Problem.

197 Observe that every function besides XOR in the table has a (small) gap between the

198 circuit lower and upper bound, and the “ $\Omega(1)$  Fanout” column ends with a question mark

199 (?). This is because XOR is the *only* listed function for which we know the *exact* circuit

200 complexity and an optimal circuit characterization. The other “ $\Omega(1)$  Fanout” entries above

201 are extrapolated by assuming that their respective DeMorgan *upper bound* constructions

---

<sup>5</sup> Some of listed bounds are in  $\mathcal{U}_2$ , the basis consisting of every binary Boolean function besides  $\text{XOR}_2$  and  $\neg\text{XOR}_2$ . For non-degenerate functions besides  $f(x) = \neg x$ ,  $\mathcal{U}_2$  and  $\mathcal{D}$  are equivalent in terms of size. The multiplexer lower bound of [33] is for the  $\mathcal{B}_2$ , the basis of all binary Boolean functions, but it also serves as the best known lower bound in  $\mathcal{D}$ .

■ **Table 1** Explicit Functions with Circuit Lower Bounds in the DeMorgan Basis

| Function(s)              | Lower Bound | Upper Bound        | $\Omega(1)$ | Fanout   | Source(s) |

|--------------------------|-------------|--------------------|-------------|----------|-----------|

| XOR                      | $3(n - 1)$  | =                  | $3(n - 1)$  | NO       | [39]      |

| Sum Mod 4                | $4n - O(1)$ | $5n - O(1)$        | NO?         | [44]     |           |

| Sum Mod $2^k$            | $4n - O(1)$ | $7n - o(n)$        | NO?         | [44]     |           |

| Multiplexer              | $2(n - 1)$  | $2n + O(\sqrt{n})$ | YES?        | [34, 24] |           |

| Well-Mixed               | $5n - o(n)$ | poly               | MAYBE?      | [27, 21] |           |

| Weighted Sum of Parities | $5n - o(n)$ | $5n + o(n)$        | YES?        | [1]      |           |

202 are optimal. For instance, Zwick conjectured that optimal circuits computing the Sum Mod

203 4 ( $\text{MOD}_4$ ) function are “shaped like” ternary full-adder blocks [44]. If this conjecture is

204 true, then  $\text{MOD}_4$ -Simple Extension can be solved in poly-time since such circuits satisfy

205 the properties of our Main Lemma. Since the  $\text{MOD}_{2^k}$  functions are computed similarly, we

206 conjecture that exactly characterizing the optimal circuits for Zwick’s functions would yield

207 efficient Simple Extension Solvers — not a proof of ETH-hardness for total MCSP.

208 However, we do have linear lower bounds for functions whose best known constructions

209 have non-constant fanout: the multiplexing function (**MUX**) contains sub-circuits which are

210 reused a logarithmic number of times [24]. In contrast to **XOR** however, the bounds for **MUX**

211 are not tight. The best lower bound is  $2(n - 1)$ , given by Paul [33].

212 **Future Directions.** The most obvious next step is to either (1) obtain total characterization

213 of the Multiplexer or (2) extend our Simple Extension Solver to handle circuits with super-

214 constant fanout. Neither of these tasks seems easy, but also they have not been subject to

215 intensive research the way that super-linear circuit lower bounds and hardness of MCSP

216 have. We hope that connecting these kinds of results to ETH-hardness of MCSP provides

217 new perspective and motivation.

218 Ilango’s MCSP\* result has also formed the basis for several hardness results in other

219 models of computation such as formulas and branching programs [19, 9, 10]; could one show

220 that the simple extension problem for formulas or branching programs is hard? These other

221 models of computations may prove easier to work with than unrestricted circuits. They also

222 enjoy superlinear lower bounds thereby bypassing our algorithm. Investigating the simple

223 extension problem in these settings would provide insight into the feasibility of the approach

224 in the circuit setting.

225 We conclude this section with a discussion of the simple extension problem in general.

226 Despite having only been studied as a tool for proving hardness of MCSP thus far, it may be of

227 independent interest. For example, while hardness of time-bounded Kolmogorov complexity

228 is tightly connected to the existence of one-way functions, hardness of MCSP has much weaker

229 quantitative connections [28, 36]. The  $f$ -Simple Extension Problem is more “structured”

230 than MCSP and easily reduces to it, so hardness assumptions about  $f$ -Simple Extension

231 Problem are stronger. Could such assumptions imply one-way functions?

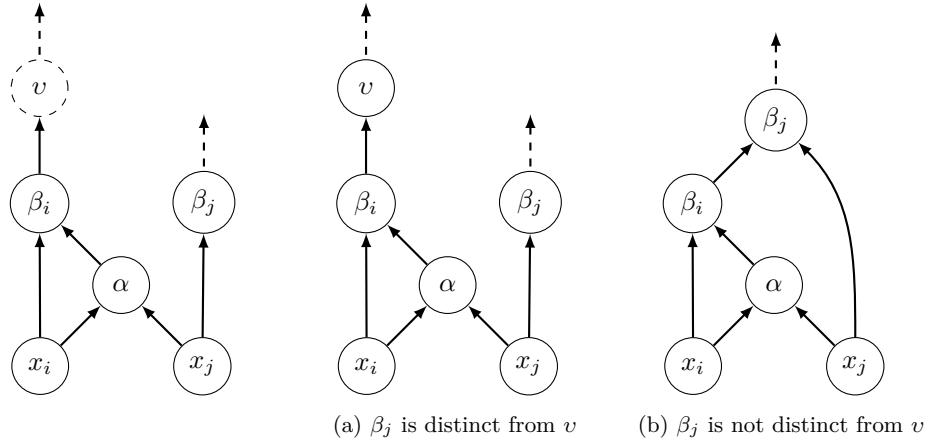

## 232 1.4 Proof Techniques

### 233 1.4.1 The Structure of Optimal XOR Circuits

234 Similar to [25], we show that *every* optimal  $(\neg)\text{XOR}_n$  circuit over the DeMorgan basis

235 partitions into trees of  $(n - 1)$  sub-circuits computing  $(\neg)\text{XOR}_2$  — even when NOT gates are

236 free. The structure of optimal circuits computing the **XOR**-function is a crucial ingredient for

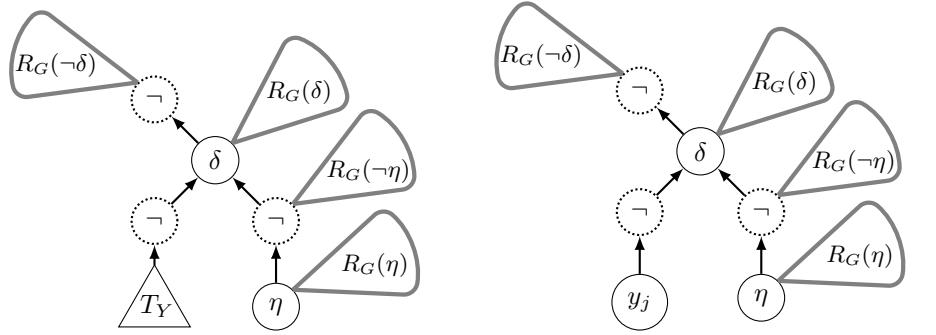

**Figure 1** An example of the binary tree structure of optimal circuits computing  $\text{XOR}_6$ . The left sub-figure depicts possible  $(\neg)\text{XOR}_2$  blocks in the Red'kin and DeMorgan Bases. Notice each optimal Red'kin circuit is an optimal DeMorgan circuit, but not vice-versa. The right sub-figure depicts that the arrangement of  $\text{XOR}_2$  blocks that make up  $\text{XOR}_6$  circuits are shared by both bases.

237 ruling it out as a candidate function. We carry out an elementary but intricate case analysis

238 of restricting and eliminating gates from optimal  $\text{XOR}$  circuits. Essentially we extract more

239 information from the proof of Schnorr's lower bound by using it to identify "templates"

240 that must be found in *any* optimal  $\text{XOR}$  circuit. We push this process to the limit, fully

241 characterizing the "shape" of all such circuits. Specifically,

- 242 ■ Schnorr's proof is essentially a technical lemma which says that any one-bit restriction will

243 eliminate at least 3 costly gates [39]. This means that at the bottom level of every optimal

244  $\text{XOR}$  circuit, any variable must be fed into two distinct costly gates, and furthermore, one

245 of these two must be fed into another costly gate. Any deviation from these properties will

246 violate essential properties of the  $\text{XOR}$ -function, such as " $\text{XOR}$  depends on all the input

247 bits." Via a basic inductive argument and the fact that  $\text{XOR}$  is downward self-reducible,

248 Schnorr's lower bound follows:  $CC(\text{XOR}_n) \geq 3(n - 1)$ .

- 249 ■ Schnorr's proof leaves the local structure of the optimal circuit computing  $\text{XOR}$  "open."

250 Namely, it does not provide any information about the other inputs of the costly gates

251 or where their outputs connect to the rest of the circuit, since we consider fan-in 2 and

252 unbounded fan-out. However, we know that  $\text{XOR}$  circuit has a matching upper-bound of

253  $3(n - 1)$ . In particular, this means *each one-bit restriction cannot remove more than 3

254 gates*. We also know that *each variable in optimal  $\text{XOR}$ -circuits must be read twice*.

- 255 ■ We leverage these two properties to show that in every optimal  $\text{XOR}$  circuit, any two

256 distinct input variables  $x_i$  and  $x_j$  must be fed into a block  $\mathcal{B}$  as shown in the left sub-figure

257 of Figure 1. Specifically, we argue that any deviations from the block will violate at

258 least one of the properties via exhaustive case analyses of gate elimination steps. Finally,

259 we argue that this block  $\mathcal{B}$  must compute either  $\text{XOR}_2$  or  $\neg\text{XOR}_2$  and apply a basic

260 inductive argument to obtain the desired structural characterization of any optimal circuit

261 computing  $\text{XOR}_n$  as depicted in the right sub-figure of Figure 1.

- 262 Besides the linear size for optimal circuits computing  $\text{XOR}$ , our structural theorem yields two

263 more properties that rule out  $\text{XOR}$  as a candidate function for MCSP-hardness via Simple

264 Extension. That is, for optimal circuits computing  $\text{XOR}_n$ , (1) *the maximum fan-out is a

265 constant*, and (2) *the number of such optimal circuits up to permutation of variables, is  $2^{O(n)}$* .

■ **Algorithm 1** Informal Simple Extension Solver, taking input  $n \in \mathbb{N}$ ,  $g \in \mathcal{F}_{n+m}$

---

```

1: if there is no key to  $f$  in  $g$  or  $g$  is degenerate then

2:   return False

3:  $\triangleright$  If the above tests pass, then  $g$  is a non-degenerate extension of  $f$ . It remains to check

simplicity.

4: for each isomorphism class  $\mathcal{C}$  of open optimal circuits for  $f$  do

5:    $F \leftarrow$  an arbitrary element of  $\mathcal{C}$  with all gates labelled in topological order

6:   label the open nodes of  $F$  by an arbitrary permutation of  $x_1, \dots, x_n$

7:   for each reverse elimination  $E$  that adds exactly  $m$  costly gates to  $F$  do

8:      $\tilde{G} \leftarrow \text{Decode}(F, E)$

9:     if  $\text{tt}(\tilde{G}) \simeq \text{tt}(g)$  then  $\triangleright$  Test using the procedure of Theorem 26.

10:    return True

11: return False

```

---

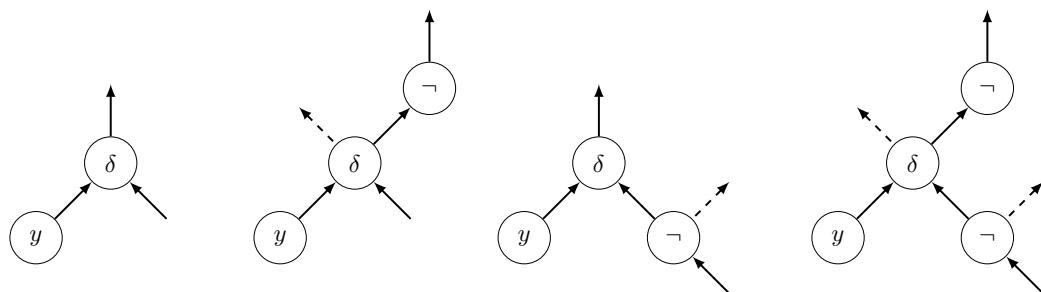

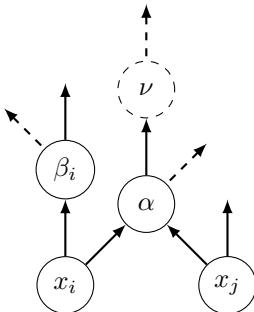

266 **1.4.2 A Fixed-Parameter Tractable Simple Extension Solver**

267 It is easy to see that the approach of solving the Simple Extension Problem for  $\text{XOR}_n$  via

268 brute-forcing over all possible circuits of size  $CC(f) + m$  is super-polynomial in terms of

269 the length of the input truth-tables. Using the following ingredients, we design Algorithm

270 1 below, a Fixed-Parameter Tractable (FPT) algorithm for the Simple Extension problem

271 that depends on the following three parameters: (1) the number of optimal circuits for  $f$  (up

272 to isomorphism & permutation of variables), (2) the maximum fanout of any node in any

273 optimal circuit for  $f$ , and (3)  $CC(f)$ .

274 **Structured Simple Extension Circuits.** By analyzing the *behavior* of optimal simple ex-

275 tension circuits under gate elimination, we are able to characterize the *structure* of *every*

276 optimal circuit computing a simple extension. By definition, if  $g$  is a simple extension of

277  $f$  then there are restrictions of  $g$ 's added variables (called *extension variables* and denoted

278  $y_i$ ) that yield  $f$ . We call such a restriction a *key* to  $f$  in  $g$ . We first show that *circuits*

279 *obtained by partially restricting with a key are themselves optimal simple extension circuits for*

280 *intermediate extensions*. Building on this, we then develop convenient *all-stops restrictions*

281 that order substitutions and simplification steps with the following properties: (1) *single-bit*

282 *substitutions from this key in the given order eliminate exactly one costly gate at each step*, (2)

283 *there exists such an all-stops restriction for any optimal circuit computing a simple extension*

284 (Lemma 17).

285 Combining these tools, we inductively show a robust structure arises in optimal simple

286 extension circuits: *each extension variable occurs in an isolated read-once subformula that*

287 *depends only on other extension variables* (referred to as the *Y-trees*). Formally,

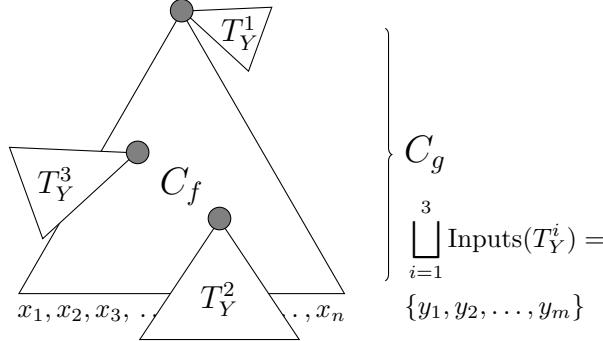

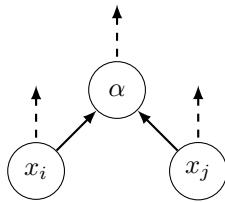

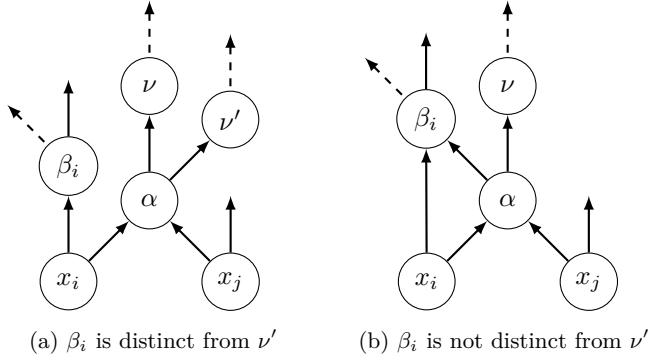

288 ▶ **Definition 1** (Y-Tree Decomposition). *Let  $G$  be a circuit with two distinguished sets of*

289 *inputs: base variables  $X$  and extension variables  $Y$ . A Y-Tree Decomposition of  $G$  is a set*

290 *of triples  $\langle \gamma, b, T \rangle$  where  $\gamma$ —referred to as a combiner—is a costly gate of  $G$ , bit  $b \in \{0, 1\}$*

291 *designates an input of  $\gamma$ , and  $T$  is a sub-circuit of  $G$  rooted at the  $b$  child of  $\gamma$  such that*

- 292 1. *Each  $T$  is a read-once formula in only extension variables  $Y$ .*

293 2. *Each  $y_i \in Y$  appears in at most one  $T$ .*

294 3. *Each  $T$  is isolated in  $G$  — gate  $\gamma$  is the unique gate reading from  $T$ , and it only reads*

295 *the root of  $T$ .*

296 4. *The sub-circuit of  $G$  rooted at the  $\neg b$  child of  $\gamma$  contains at least one  $X$  variable.*

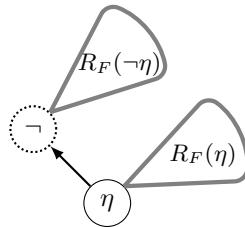

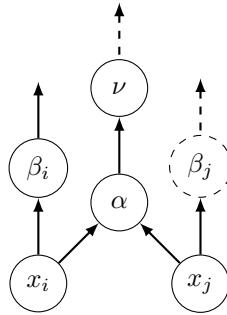

■ **Figure 2** An example of a Y-Tree Decomposition of size three.

297     The size of a decomposition is the number of tuples — Y-trees and their associated

298     combiner gates — present in the decomposition. The weight of a Y-tree decomposition is the

299     number of extension variables that are read in some  $T$ . We say a Y-tree decomposition is total

300     if its weight is  $|Y|$ , i.e. every extension variable appears. An example Y-tree decomposition

301     of size three is depicted in Figure 2, where the shaded circles represent the circuitry around

302     each combiner  $\gamma$  connecting each  $T_Y$  to the rest of the circuit.

303     When gate elimination is performed with a total key, these added Y-trees and their

304     combiners are pruned to reveal an embedded optimal circuit for the base  $f$  function. We get

305     the following structural insight: *every optimal simple extension circuit has a total Y-tree*

306     decomposition. This decomposition forms the basis of our strategy: we brute force over every

307     optimal base circuit and try to “splice in” every possible Y-tree.

308     **Encoding & Decoding the “Grafts” in a Y-Tree Decomposition.** To ensure we can

309     efficiently construct these candidate simple extension circuits, we devise an encoding scheme

310     and corresponding decoding algorithm which efficiently captures the difference in local

311     neighborhoods after each new Y-tree is spliced on top of an existing gate or input. Our final

312     encoding must be  $O(n + m)$  bits long to ensure brute-force runs in  $2^{O(n+m)}$ . We present our

313     encoding as a communication problem to clarify the overhead and constraints involved.

314     Suppose  $g$  is a simple extension of  $f$  and Alice knows  $G$ , an optimal circuit for  $g$ . Alice

315     can obtain an optimal circuit  $F$  computing  $f$  by simply restricting the  $y$ -variables of  $G$  with

316     a key and performing gate elimination. Now consider the following communication problem:

317     Bob (i.e., line 5 of Algorithm 1) knows  $F$ , and Alice would like to send him  $G$  using as

318     few bits as possible. Because  $g$  is a simple extension of  $f$ , Alice can compute the Y-tree

319     decomposition of optimal circuit  $G$ . The idea is to send Bob a sequence of instructions that

320     tell him exactly how to graft each Y-Tree of  $G$  onto the gates of  $F$ , where all information is

321     encoded relative to isomorphism-invariant properties of  $F$ .

322     **Speeding Up Via Truth-table Isomorphism.** Brute-forcing over the total encodings de-

323     scribed above is still incredibly inefficient. Since each Y-tree is a read-once formula in the

324     added  $m$  variables there are least  $C_{m-1} \cdot m!$  such explicit Y-trees, where  $C_a$  is the  $a^{th}$  Catalan

325     number [42]. The dominating term— $m!$ —comes from permuting the labels of the variables.

326     The same issue arises if our base function  $f$  is symmetric: the number of optimal  $f$  circuits

327     is  $\Omega(n!)$ .

328     We sidestep this issue and drastically improve the speed of brute-force search. If we

329     “incorrectly” assign variables in the base circuit or in the Y-trees, the result is a circuit for

330 a Boolean function that is *truth-table isomorphic* to  $g$ , i.e. their truth-tables are the same

331 up to a permutation of the inputs. If  $h$  and  $g$  are truth-table isomorphic then they have

332 the same circuit complexity. Thus it suffices to brute-force over unlabeled (“open”) base

333 circuits and  $Y$ -trees, assign variables to inputs arbitrarily, generate each circuit’s truth table,

334 and check if it is truth-table isomorphic to  $g$ . This final step is feasible since truth-table

335 isomorphism testing can be done in polynomial time [30].

336 This results in our final algorithm, which runs in time  $O(|L| \cdot 2^{O(\ell(s+m))})$  where  $|L|$  is the

337 number of optimal base  $f$  circuits up to permutation of variables,  $\ell$  is the maximum fanout

338 in any of those base circuits, and  $s = CC(f)$ . As discussed above, for XOR these parameters

339 are all sufficiently small and hence XOR-Simple Extension is in P.

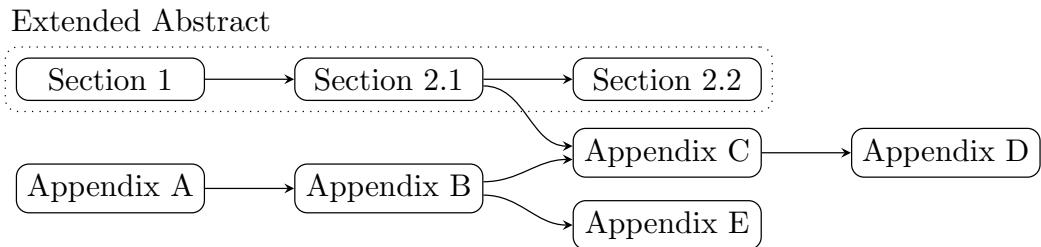

### 340 1.4.3 Paper Outline

341 The paper is laid out as follows. Section 2 explores the implicit reduction present to  $f$ -SEP in

342 the ETH-hardness proof for MCSP\* in [18]. This discussion yields our Main Observation and

343 motivates our study of  $f$ -SEP and circuit structures. It, in conjunction with this introduction,

344 constitutes an extended abstract of our paper.

345 Appendix A and Appendix B formally define circuits and gate elimination respectively.

346 In Appendix C, we establish that every optimal circuit computing simple extensions are

347 highly structured: they can be decomposed into  $Y$ -trees. This observation forms the basis of

348 our Main Result, a fixed parameter tractable algorithm for  $f$ -SEP, in Appendix D. Finally,

349 in Appendix E, we extend Kombarov’s characterization of optimal XOR circuits in  $\mathcal{R}$  to  $\mathcal{D}$ ,

350 in order to apply our Main Theorem to XOR-SEP.

351 The dependence between sections varies. For example, Appendix E is independent of the

352  $f$ -SEP material like Section 2 and Appendix C. To aid the reader, we provide a reading order

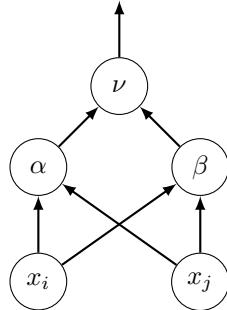

in Figure 3.

353 **Figure 3** The structure of our paper. Sections 1 and 2 form an extended abstract. An incoming

354 arrow indicates that the material depends on the previous section.

355

## 356 2 Revisiting ETH hardness for MCSP\* via Simple Extensions

357 We re-examine the proof that MCSP\* is ETH-hard from [18]. Our aim is to better understand

358 the reduction from  $2n \times 2n$  Bipartite Permutation Independent Set (BPIS) to the Partial  $f$

359 Simple Extension problem ( $f$ -SEP\*).

### 360 2.1 The $f$ -Simple Extension Problem

361 We give formal definitions of simple extensions and its associated decision problem. We first

362 define non-degeneracy of a Boolean function.

361 ► **Definition 2.** A function  $f \in \mathcal{F}_n$ , the set of Boolean functions on  $n$  variables, depends

362 on its  $i^{th}$  variable,  $x_i$ , if there exists an input  $\alpha \in \mathcal{F}_n$  such that  $f(\alpha) \neq f(\alpha \oplus e_i)$ , where  $e_i$

363 denotes the Boolean vector that is 0 everywhere except for a 1 at index  $i$  and  $\oplus$  is bitwise XOR.

364 If  $f$  depends on all of its variables, then we say  $f$  is a non-degenerate function. Conversely,

365 we say  $f$  is a degenerate function if it does not depend on at least one variable.

366 We now define simple extension as

367 ► **Definition 3.** Let  $f \in \mathcal{F}_n$  be non-degenerate. A simple extension of  $f$  is either  $f$  itself or

368 a function  $g \in \mathcal{F}_{n+m}$  satisfying:

- 369 1.  $g$  is a non-degenerate function,

- 370 2.  $CC(g) = CC(f) + m$ , and

- 371 3. there exists a setting  $k \in \{0, 1\}^m$ , called a key, such that for all  $x \in \{0, 1\}^n$ ,  $g(x, k) = f(x)$ .

372 We denote the first  $n$  inputs of  $f$  and  $g$  by  $x_1, \dots, x_n$  and will refer to the extra  $m$  inputs

373 of  $g$  as *extension variables* and refer to them as  $y_1, \dots, y_m$ . From the definition of simple

374 extension above, we define the following decision problem.

375 ► **Problem 1** ( $f$ -SEP). Let  $f$  be a sequence of Boolean functions  $\{f_n\}_{n \in \mathbb{N}}$  such that each  $f_n$

376 is a non-degenerate function in  $\mathcal{F}_n$ . The  $f$ -Simple Extension Problem is defined as follows:

377 Given  $n \in \mathbb{N}$  and  $tt(g)$ —the truth tables of a binary function  $g \in \mathcal{F}_{n+m}$ —decide whether  $g$  is

378 a simple extension of  $f_n$ .

379 We extend this to partial functions,

380 ► **Problem 2** ( $f$ -SEP\*). Given  $n \in \mathbb{N}$  and a partial  $tt(g)$ , decide whether any completion of

381 the truth table is a simple extension of  $f_n$ .

## 382 2.2 An Explicit Reduction BPIS from to $f$ -SEP\*

383 Recall the formulation of BPIS from [18],

384 ► **Problem 3** (BPIS). The  $2n \times 2n$  Bipartite Permutation Independent Set is defined as

385 follows: Given  $G = (V, E)$  a directed graph with vertex set  $V = [n] \times [n]$ . Decide whether

386 there exists a permutation  $\pi : [2n] \rightarrow [2n]$  such that:

- 387 1.  $\pi([n]) = [n]$ ,

- 388 2.  $\pi(\{n + i : i \in [n]\}) = \{n + i : i \in [n]\}$ ,

- 389 3. if  $((j, k), (j', k')) \in E$ , then either  $\pi(j) \neq k$  or  $\pi(j' + n) \neq k' + n$

390 If the Exponential Time Hypothesis holds, then BPIS cannot be solved much faster than

391 brute-forcing over all  $2^{o(n \log n)}$  permutations [29]. BPIS is a natural problem to show hardness

392 of circuit size problems since there are  $O(2^{s \log s})$  circuits of size  $s$ . Reducing from BPIS

393 implies, assuming ETH, that our problem can not be solved much faster than by brute-forcing

394 over all possible circuits.

395 The reduction from BPIS to  $f$ -SEP\*, as it appears as part of the original proof, is somewhat

396 *implicit*; the target problem, as written, could be described more simply as “determine whether

397 a partial truth table is ever consistent with a monotone read-once formula.” Since this is *easy*

398 for total functions [2, 13], this view of the reduction cannot help us to extend the reduction

399 technique to total MCSP. We will need the more general  $f$ -SEP and by reframing Ilango’s

400 proof we gain insight into how it might extend to total functions.

401 The connection to  $f$ -SEP\* is *explicitly* stated, however, in the introduction of [18]. Here,

402 the reduction is identified with  $OR_{4n}$ -SEP\* where each  $z$  variable is an extension variable.

## 23:12 Simple Circuit Extensions for XOR in PTIME

403 This is true, though non-degenerate functions computed by read-once formulas are simple

404 extensions of *any* of their non-degenerate restrictions. When framing the reduction to  $f$ -SEP\*

405 explicitly, we find it more compelling to choose a different function  $\hat{f}$ , whose truth table

406 is given by  $\bigvee_{i \in [2n]} (y_i \wedge z_i)$  — because using  $\hat{f}$  makes the intuitive description of Ilango's

407 technique "reverse gate elimination" an obvious property of the reduction. Under this framing,

408 the extension variables will instead be the  $x$  variables in Ilango's original proof. Despite

409 this, fixing  $f$  to be  $\text{OR}_{4n}$  is *not* arbitrary; afterwards, we discuss what insight it provides.

410 Informally, the two choices of base function provide distinct "channels" for ETH to imply

411 hardness of  $f$ -SEP\*.

412 **Structural Lemmas** To encode BPIS in  $\hat{f}$ -SEP\*, we first prove two lemmas which were

413 essentially proven in tandem in [18] as Lemma 16. We separate them out here and stay faithful

414 to the original arguments. Like Lemma 16, these lemmas establish structural properties of

415 circuits computing our base function  $\hat{f}$  and our eventual output  $\hat{g}$ .

416 ▶ **Lemma 4.** *Let  $\hat{f} : \{0, 1\}^{2n} \times \{0, 1\}^{2n} \rightarrow \{0, 1\}$  be the Boolean function computed by

417  $\bigvee_{i \in [2n]} (y_i \wedge z_i)$ . If  $\psi$  be an optimal normalized<sup>6</sup> formula computing  $\hat{f}$ , then  $\psi$ , as a formula,

418 is equal to  $\bigvee_{i \in [2n]} (y_i \wedge z_i)$ .*

419 In particular, the only difference between two distinct optimal circuits for  $\hat{f}$  is which binary

420 tree of fanin 2  $\vee$  gates is used.

421 **Proof.** Observe that  $\psi$  must read all of its input variables and furthermore must do so

422 positively. This is because (1)  $f$  depends on all of its variables and is monotone in them, and

423 (2)  $\psi$  is normalized and thus no  $\neg$  gates can appear internally in the circuit. We note that  $\psi$

424 must use a total of  $4n - 1$  gates since  $f$  is non-degenerate on  $4n$  variables computable. We

425 see that  $\psi$  must contain at least  $2n - 1$   $\vee$  gates: substituting  $z = 1^{2n}$  and simplifying yields

426 a monotone read once formula computing  $\text{OR}_{2n}(y_1, \dots, y_{2n})$  which must consist of  $2n - 1$   $\vee$

427 gates that appear in  $\psi$ .

428 We now argue that each  $z_i$  feeds into an  $\wedge$  gate. Assume otherwise, then observe that

429 setting  $z_i = 1$  and simplifying removes at least two gates (since  $z_1 \vee p \equiv 1 \vee p \equiv 1$ ). The

430 resulting read once formula for  $\hat{f}|_{z_i \leftarrow 1}$  uses at most  $4n - 3$  gates. This is a contradiction

431 since  $\hat{f}|_{z_i \leftarrow 1}$  still depends on all of its remaining  $4n - 1$  variables: it cannot be computed by

432 a circuit with fewer than  $4n - 2$  gates.

433 We now argue the other input to the  $\wedge$  gate fed by  $z_i$  is  $y_i$ . Assume otherwise. Notice

434 that since  $\psi$  is read-once, setting  $z_i \leftarrow 0$  simplifying disconnects the other input to  $\wedge$  gate

435 and thus removes dependence on any variables it depends on. However,  $\hat{f}|_{z_i \leftarrow 0}$  still depends

436 on all of its variables besides  $y_i$ . Thus the  $\wedge$  gate can only read  $y_i$ .

437 Since each  $z_i$  and  $y_i$  feed a distinct  $\wedge$  gate, there are at least  $2n \wedge$  gates. Since there are

438  $4n - 1$  total gates, and at least  $2n - 1$   $\vee$  gates, we know that these  $\wedge$  gates are the only  $\wedge$

439 gates that appear. Thus the remainder of the circuit is a binary tree of  $2n - 1$   $\vee$  gates whose

440  $2n$  leaves are the  $2n \wedge$  gates. ◀

441 Having established the structure of optimal circuits computing  $\hat{f}$  we can further restrict

442 its simple extensions. Extra restrictions to the truth table enforce that extension variables

443 must be spliced into the circuit using  $2n$  additional  $\vee$  gates that each read a different  $y_i$ .

---

<sup>6</sup> A formula is normalized if all negations are pushed down to the input level. Normalization does not affect the size of the formula, and thus  $f$ -SEP\* still reduces to MCSP\* even if we restrict ourself to normalized formulas.

■ **Table 2** BPIS requirements and the corresponding restrictions on  $\hat{g}$

| BPIS Requirement on $\sigma$                                                              | Corresponding $\hat{g}$ Restriction                                                          | Impact If $\pi$ Violates                                                  |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| $\sigma(\{1, \dots, n\}) = \{1, \dots, n\}$                                               | $\text{OR}_n(x_1, \dots, x_n)$ when $z = 1^n 0^n$ and $y = 0^{2n}$                           | If $\pi(i) = j \geq n$ , then $z_j \leftarrow 0$ removes $x_i$ in $C_\pi$ |

| $\sigma(\{n+1, \dots, 2n\}) = \{n+1, \dots, 2n\}$                                         | $\text{OR}_n(x_{n+1}, \dots, x_{2n})$ when $z = 0^n 1^n$ and $y = 0^{2n}$                    | As above, $C_\pi _{z_j \leftarrow 0}$ will not depend on $x_i$            |

| If $((j, k), (j', k')) \in E$ then $\sigma(j) \neq k$ or $\sigma(n+j') \neq \sigma(n+k')$ | 1 if $(x, y, z) = (e_k e_{k'}, 0^{2n}, e_j e_{j'})$ where $\exists ((j, k), (j', k')) \in E$ | $C_\pi$ wrongly outputs 0                                                 |

444 This pairing of each  $y_i$  with a different  $x_j$  will define a permutation in which we can encode

445 BPIS solutions.

446 ▶ **Lemma 5.** *Let  $g : \{0, 1\}^{2n} \times \{0, 1\}^{2n} \times \{0, 1\}^{2n} \rightarrow \{0, 1\}$  be any simple extension of  $\hat{f}$

447 satisfying the following conditions:*

$$448 \quad g(x, y, z) = \begin{cases} \hat{f}(y, z) & \text{if } x = 0^{2n} \\ \text{OR}_{2n}(z_1, \dots, z_{2n}) & \text{if } x = 1^{2n} \\ \text{OR}_{4n}(x_1, \dots, x_{2n}, y_1, \dots, y_{2n}) & \text{if } z = 1^{2n} \\ 0 & \text{if } z = 0^{2n} \end{cases}$$

449 If  $\phi$  is an optimal normalized formula computing  $g$  then there exists a permutation  $\pi : [2n] \rightarrow$

450  $[2n]$  such that  $\phi$  equals, as a formula,  $\bigvee_{i \in [2n]} ((x_{\pi(i)} \vee y_i) \wedge z_i)$ .

451 **Proof.** Since  $g(x, y, z) = \hat{f}(y, z)$  when  $x = 0^{2n}$ , we know that  $\phi$  must read all  $y$  and  $z$

452 variables positively. Similarly, all  $x$  variables must be read positively, since  $g(x, y, 1^{2n}) =$

453  $\text{OR}_{4n}(x_1, \dots, x_{2n}, y_1, \dots, y_{2n})$ . Note that these restrictions also imply that  $\phi$  contains exactly

454  $4n - 1 \vee$  gates and  $2n \wedge$  gates since substituting and simplifying yields optimal formulas for

455 those restrictions. From the lemma above, we know know that when setting  $x = 0^{2n}$  and

456 simplifying, we obtain a circuit structurally equivalent to  $\bigvee_{i \in [2n]} (y_i \wedge z_i)$ . Therefore  $2n \vee$

457 gates must be removed during simplification. These  $\vee$  gates cannot feed any remaining  $\vee$

458 above the  $\wedge$  gates, since otherwise setting  $x = 1^{2n}$  would fix the circuit to be 1, rather than

459  $\text{OR}_{2n}(z_1, \dots, z_{2n})$ . Similarly,  $z_i$  cannot feed any of these  $\vee$  gates, as setting  $x = 1^{2n}$  would

460 remove dependence on that  $z_i$  since the circuit is a read-once formula. Thus each  $\vee$  gate can

461 only depend on the  $x$  and  $y$  variables. Observe that each  $y_i$  must feed into one of these  $\vee$

462 gates instead of the  $\wedge$  gate fed by  $z_i$ , as otherwise when we set  $x = 1^{2n}$ , the function would

463 still depend on  $y_i$ . Since there are exactly  $2n$  additional  $\vee$  gates, and exactly  $2n$   $y$  and  $2n$   $x$

464 variables, its easy to see that each additional  $\vee$  gate must read one  $x_i$  and one  $y_j$ . Therefore,

465 as a formula,  $\phi$  must be  $\bigvee_{i \in [2n]} ((x_{\pi(i)} \vee y_i) \wedge z_i)$  for some permutation  $\pi$ . ◀

466 **An Explicit Reduction** We now provide an explicit reduction from BPIS to  $\hat{f}$ -SEP\*. Given an

467 instance  $G$  of BPIS we output  $4n$  and the partial truth-table for a function  $\hat{g}$  that is consistent

468 with the requirements of Lemma 5. We add three additional restrictions (listed in Table 2) to

469 ensure that any permutation  $\pi$ , whose corresponding circuit  $C_\pi \equiv \bigvee_{i \in [2n]} ((x_{\pi(i)} \vee y_i) \wedge z_i)$

470 is consistent with  $\hat{g}$ , is also a solution for  $G$  (and vice versa). All other rows of the truth table

471 are left undefined (e.g. as  $\star$ ). We summarize the requirements for any valid BPIS solution  $\sigma$ ,

472 the corresponding restriction, and how it enforces the requirement on  $\pi$  in Table 2.

473 This completes the reduction as any  $\sigma$  satisfying BPIS for  $G$  can be used to construct

474 a read-once circuit consistent with  $\hat{g}$  and vice versa. The arguments verifying this are the

475 same as in [18], and we refer the reader there for the full details.

476 ▶ **Lemma 6.** BPIS reduces to  $\hat{f}$ -SEP\* in  $2^{O(n)}$  time.

477 **The Original Framing** In its introduction, [18] identifies  $\hat{g}$  as a simple extension of  $\text{OR}_{4n}$ .

478 Under this lens, the hardness comes from determining which  $\text{OR}_{4n}$  base circuit can have the

479  $z$  extension variables added. The additional truth-table restrictions on  $\hat{g}$  force each  $z_i$  to be

480 spliced in a particular way adjacent to  $y_i$ . Assuming ETH, there are  $\Omega(n!)$  optimal base

481  $\text{OR}_{4n}$  circuits that must be checked via brute-force.

482 **Implicit Circuit Lower Bounds & Enumeration of Optimal Circuits** From both presenta-

483 tions, we see that leveraging  $f$ -SEP involves explicit circuit size lower bounds. Indeed, both

484 Lemma 4 and Lemma 5 prove formula lower bounds for specific non-degenerate functions.

485 However, in a sense, circuit lower bounds are intrinsic to the reduction itself. This connection

486 can be made rigorous: the reduction can be used to produce explicit Boolean functions which

487 enjoy non-vacuous lower bounds. On no instance of BPIS, the reduction outputs a partial

488 truth table where every completion is non-degenerate but *not* a simple extension. Hence, the

489 circuit complexity of these completions is not the vacuous  $6n - 1$  lower bound obtained by

490 knowing that functions produced are non-degenerate.

491 Furthermore, the reduction did not solely rely on the circuit complexity of  $\hat{f}$  and  $\hat{g}$ .

492 Lemmas 4 and 5 *tightly control* how base circuits and their extensions can be arranged;

493 and this is pivotal for encoding BPIS permutations. This structural requirement can be

494 formalized by observing the reduction is also an efficient *Levin reduction*.

495 Recall, from [32], that a Levin reduction is a many-one reduction that also efficiently

496 maps witnesses, not just problem instances. More precisely, let  $R$  be a set of ordered pairs

497  $(x, w)$  where  $x$  is a yes-instance of a problem and  $w$  is an accompanying certificate. We define

498  $L_R$ , the language defined by  $R$ , to be the set of elements  $x$  such that  $(x, w) \in R$  for some  $w$ .

499 Then a Levin reduction between two languages  $A$  and  $B$  is an efficient many-one reduction  $r$

500 between problem instances paired with two efficient mappings  $m, \ell$  between instance-witness

501 pairs that satisfy (1) if  $(x, w) \in R_A$  then  $(r(x), m(x, w)) \in R_B$  and (2)  $(t(x), w) \in R_B$  implies

502  $(x, \ell(x, w)) \in R_A$ .

503 For BPIS, the witnesses for an instance are simply the valid permutations  $\sigma$  and witnesses

504 for  $\hat{f}$ -SEP are optimal circuits computing the extension. Let  $\mathcal{R}_{\text{BPIS}}$  and  $\mathcal{R}_{\hat{f}\text{-SEP}^*}$  be the

505 sets of ordered pairs consisting of problem instances and all of their witnesses as described.

506 The reduction admits linear time mappings between witnesses: given  $\sigma$ , simply construct

507  $\bigvee_{i \in [2n]} ((x_{\sigma(i)} \vee y_i) \wedge z_i)$  and given a circuit for  $\hat{g}$ , simply read off the permutation from the

508  $x$  variables.

509

---

References

- 510 1 Kazuyuki Amano and Jun Tarui. A well-mixed function with circuit complexity  $5n$ : Tightness

511 of the lachish–raz-type bounds. *Theoretical computer science*, 412(18):1646–1651, 2011.

- 512 2 Dana Angluin, Lisa Hellerstein, and Marek Karpinski. Learning read-once formulas with

513 queries. *J. ACM*, 40(1):185–210, 1993. doi:10.1145/138027.138061.

- 514 3 Vikraman Arvind and Yadu Vasudev. Isomorphism testing of boolean functions computable

515 by constant-depth circuits. *Inf. Comput.*, 239:3–12, 2014. URL: <https://doi.org/10.1016/j.ic.2014.08.003>, doi:10.1016/J.IC.2014.08.003.

- 516 4 Eric Blais, Clément L Canonne, Igor C Oliveira, Rocco A Servedio, and Li-Yang Tan. Learning

517 circuits with few negations. *arXiv preprint arXiv:1410.8420*, 2014.

- 518 5 Norbert Blum and Martin Seysen. Characterization of all optimal networks for a si-

519 multaneous computation of AND and NOR. *Acta Informatica*, 21:171–181, 1984. doi:

520 10.1007/BF00289238.

- 521 6 Mahdi Cheraghchi, Valentine Kabanets, Zhenjian Lu, and Dimitrios Myrisiotis. Circuit lower

522 bounds for mcsps from local pseudorandom generators. *ACM Transactions on Computation

523 Theory (TOCT)*, 12(3):1–27, 2020.

- 524 7 Thomas H. Cormen, Charles E. Leiserson, Ronald L. Rivest, and Clifford Stein. *Introduction

525 to Algorithms, 3rd Edition*. MIT Press, 2009. URL: <http://mitpress.mit.edu/books/introduction-algorithms>.

- 526 8 William Feller and Philip M Morse. An introduction to probability theory and its applications.

527 vol i, 1968.

- 528 9 Ludmila Glinskih and Artur Riazanov. MCSP is hard for read-once nondeterministic branching

529 programs. In Armando Castañeda and Francisco Rodríguez-Henríquez, editors, *LATIN 2022:

530 Theoretical Informatics - 15th Latin American Symposium, Guanajuato, Mexico, November

531 7-11, 2022, Proceedings*, volume 13568 of *Lecture Notes in Computer Science*, pages 626–640.

532 Springer, 2022. doi:10.1007/978-3-031-20624-5\\_38.

- 533 10 Ludmila Glinskih and Artur Riazanov. Partial minimum branching program size problem is

534 eth-hard. *Electron. Colloquium Comput. Complex.*, TR24-117, 2024. (To Appear in ITCS

535 2025). URL: <https://eccc.weizmann.ac.il/report/2024/117>, arXiv:TR24-117.

- 536 11 Alexander Golovnev, Edward A. Hirsch, Alexander Knop, and Alexander S. Kulikov. On

537 the limits of gate elimination. *J. Comput. Syst. Sci.*, 96:107–119, 2018. doi:10.1016/j.jcss.

538 2018.04.005.

- 539 12 Alexander Golovnev, Rahul Ilango, Russell Impagliazzo, Valentine Kabanets, Antonina

540 Kolokolova, and Avishay Tal. Ac0 [p] lower bounds against mcsps via the coin problem.

541 In *ICALP*, 2019.

- 542 13 Martin Charles Golumbic, Aviad Mintz, and Udi Rotics. Factoring and recognition of read-

543 once functions using cographs and normality and the readability of functions associated with

544 partial k-trees. *Discrete Applied Mathematics*, 154(10):1465–1477, 2006. URL: <https://www.sciencedirect.com/science/article/pii/S0166218X06000072>, doi:<https://doi.org/10.1016/j.dam.2005.09.016>.

- 545 14 Shuichi Hirahara. Np-hardness of learning programs and partial MCSP. In *63rd IEEE Annual

546 Symposium on Foundations of Computer Science, FOCS 2022, Denver, CO, USA, October 31

547 - November 3, 2022*, pages 968–979. IEEE, 2022. doi:10.1109/FOCS54457.2022.00095.

- 548 15 Shuichi Hirahara, Igor C. Oliveira, and Rahul Santhanam. Np-hardness of minimum circuit

549 size problem for OR-AND-MOD circuits. In Rocco A. Servedio, editor, *33rd Computational

550 Complexity Conference, CCC 2018, June 22-24, 2018, San Diego, CA, USA*, volume 102

551 of *LIPICS*, pages 5:1–5:31. Schloss Dagstuhl - Leibniz-Zentrum für Informatik, 2018. URL:

552 <https://doi.org/10.4230/LIPIcs.CCC.2018.5>, doi:10.4230/LIPIcs.CCC.2018.5.

- 553 16 Shuichi Hirahara and Rahul Santhanam. On the average-case complexity of mcsps and its

554 variants. In *32nd Computational Complexity Conference (CCC 2017)*. Schloss Dagstuhl

555 Leibniz-Zentrum fuer Informatik, 2017.

- 560 17 Yizhi Huang, Rahul Ilango, and Hanlin Ren. Np-hardness of approximating meta-complexity:

561 A cryptographic approach. *Cryptology ePrint Archive*, 2023.

- 562 18 Rahul Ilango. Constant depth formula and partial function versions of mcsp are hard. *SIAM*

563 *Journal on Computing*, 0(0):FOCS20–317–FOCS20–367, 2020. [arXiv:https://doi.org/10.](https://doi.org/10.1137/20M1383562)

564 [10.1137/20M1383562](https://doi.org/10.1137/20M1383562), doi:10.1137/20M1383562.

- 565 19 Rahul Ilango. The minimum formula size problem is (ETH) hard. In *62nd IEEE Annual*

566 *Symposium on Foundations of Computer Science, FOCS 2021, Denver, CO, USA, February*

567 *7-10, 2022*, pages 427–432. IEEE, 2021. doi:10.1109/FOCS52979.2021.00050.

- 568 20 Rahul Ilango, Bruno Loff, and Igor Carboni Oliveira. Np-hardness of circuit minimization

569 for multi-output functions. In *Electronic Colloquium on Computational Complexity (ECCC)*,

570 volume 27, page 21, 2020.

- 571 21 Kazuo Iwama and Hiroki Morizumi. An explicit lower bound of  $5n - o(n)$  for boolean circuits.

572 In Krzysztof Diks and Wojciech Rytter, editors, *Mathematical Foundations of Computer*

573 *Science 2002, 27th International Symposium, MFCS 2002, Warsaw, Poland, August 26-30,*

574 *2002, Proceedings*, volume 2420 of *Lecture Notes in Computer Science*, pages 353–364. Springer,

575 2002. doi:10.1007/3-540-45687-2\\_29.

- 576 22 Stasys Jukna. *Boolean Function Complexity - Advances and Frontiers*, volume 27 of *Algorithms*

577 and *combinatorics*. Springer, 2012. doi:10.1007/978-3-642-24508-4.

- 578 23 Valentine Kabanets and Jin-yi Cai. Circuit minimization problem. In F. Frances Yao and

579 Eugene M. Luks, editors, *Proceedings of the Thirty-Second Annual ACM Symposium on*

580 *Theory of Computing, May 21-23, 2000, Portland, OR, USA*, pages 73–79. ACM, 2000.

581 doi:10.1145/335305.335314.

- 582 24 Klein and Paterson. Asymptotically optimal circuit for a storage access function. *IEEE*

583 *Transactions on Computers*, C-29(8):737–738, 1980. doi:10.1109/TC.1980.1675657.

- 584 25 Yu A Kombarov. The minimal circuits for linear boolean functions. *Moscow University*

585 *Mathematics Bulletin*, 66(6):260–263, 2011.

- 586 26 Yu A Kombarov. Complexity and structure of circuits for parity functions. *Journal of*

587 *Mathematical Sciences*, 233:95–99, 2018.

- 588 27 Oded Lachish and Ran Raz. Explicit lower bound of  $4.5n - o(n)$  for boolean circuits. In

589 *Proceedings of the Thirty-Third Annual ACM Symposium on Theory of Computing*, STOC

590 '01, page 399–408, New York, NY, USA, 2001. Association for Computing Machinery. doi:

591 10.1145/380752.380832.

- 592 28 Yanyi Liu and Rafael Pass. On one-way functions and kolmogorov complexity. In Sandy

593 Irani, editor, *61st IEEE Annual Symposium on Foundations of Computer Science, FOCS 2020,*

594 *Durham, NC, USA, November 16-19, 2020*, pages 1243–1254. IEEE, 2020. doi:10.1109/

595 FOCS46700.2020.00118.

- 596 29 Daniel Lokshtanov, Dániel Marx, and Saket Saurabh. Slightly superexponential parameterized

597 problems. *SIAM Journal on Computing*, 47(3):675–702, 2018. [arXiv:https://doi.org/10.](https://doi.org/10.1137/16M1104834)

598 [10.1137/16M1104834](https://doi.org/10.1137/16M1104834), doi:10.1137/16M1104834.

- 599 30 Eugene M Luks. Hypergraph isomorphism and structural equivalence of boolean functions. In

600 *Proceedings of the thirty-first annual ACM symposium on Theory of computing*, pages 652–658,

601 1999.

- 602 31 William J Masek. Some np-complete set covering problems. *Unpublished manuscript*, 1979.

- 603 32 Noam Mazor and Rafael Pass. Gap MCSP is not (levin) np-complete in obfustopia. In Rahul

604 Santhanam, editor, *39th Computational Complexity Conference, CCC 2024, July 22-25, 2024,*

605 *Ann Arbor, MI, USA*, volume 300 of *LIPICS*, pages 36:1–36:21. Schloss Dagstuhl - Leibniz-

606 Zentrum für Informatik, 2024. URL: <https://doi.org/10.4230/LIPICS.CCC.2024.36>, doi:

607 10.4230/LIPICS.CCC.2024.36.

- 608 33 Wolfgang J. Paul. A 2.5 n-lower bound on the combinational complexity of boolean functions.

609 In *Proceedings of the Seventh Annual ACM Symposium on Theory of Computing*, STOC

610 '75, page 27–36, New York, NY, USA, 1975. Association for Computing Machinery. doi:

611 10.1145/800116.803750.

- 612 34 Wolfgang J. Paul. A 2.5 n-lower bound on the combinational complexity of boolean functions.

613 *SIAM J. Comput.*, 6(3):427–443, 1977. doi:10.1137/0206030.

- 614 35 NP Red'kin. Proof of minimality of circuits consisting of functional elements. *Systems Theory*

615 *Research: Problemy Kibernetiki*, pages 85–103, 1973.

- 616 36 Hanlin Ren and Rahul Santhanam. Hardness of  $kt$  characterizes parallel cryptography.

617 *Cryptology ePrint Archive*, 2021.

- 618 37 Rahul Santhanam. Pseudorandomness and the minimum circuit size problem. *LIPICS*, 151,

619 2020.

- 620 38 Jürgen Sattler. Netzwerke zur simultanen berechnung boolescher funktionen. In Peter Deussen,

621 editor, *Theoretical Computer Science, 5th GI-Conference, Karlsruhe, Germany, March 23-25,*

622 *1981, Proceedings*, volume 104 of *Lecture Notes in Computer Science*, pages 32–40. Springer,

623 1981. URL: <https://doi.org/10.1007/BFb0017293>, doi:10.1007/BFB0017293.

- 624 39 Claus-Peter Schnorr. Zwei lineare untere schranken für die komplexität boolescher funktionen.

625 *Computing*, 13(2):155–171, 1974. doi:10.1007/BF02246615.

- 626 40 Claude. E. Shannon. The synthesis of two-terminal switching circuits. *The Bell System*

627 *Technical Journal*, 28(1):59–98, 1949. doi:10.1002/j.1538-7305.1949.tb03624.x.

- 628 41 B. A. Trakhtenbrot. A survey of russian approaches to perebor (brute-force searches) algorithms.

629 *Annals of the History of Computing*, 6(4):384–400, 1984. doi:10.1109/MAHC.1984.10036.

- 630 42 J. H. van Lint and R. M. Wilson. *Recursions and generating functions*, page 109–1311.

631 Cambridge University Press, 1992.

- 632 43 Ingo Wegener. *The Complexity of Boolean Functions*. Wiley-Teubner, 1987.

- 633 44 Uri Zwick. A  $4n$  lower bound on the combinational complexity of certain symmetric boolean

634 functions over the basis of unate dyadic boolean functions. *SIAM Journal on Computing*,

635 20(3):499–505, 1991.

636 **A Circuits**

637 In this section, we precisely define Boolean circuit complexity and accompanying notions

638 related to the “shapes” and “parts” of circuits. These definitions are straightforward, but

639 the details matter because we are working with *general* circuits and functions of *linear* size

640 complexity. We cannot, for example, afford to layer circuits or put them into negation normal

641 form (NNF, all NOT-gates on the inputs) because size-optimal circuits do not (in general)

642 obey these restrictions. In particular, optimal circuits for XOR are neither layered nor in

643 NNF (Theorem 37). We will require normal forms that are *free* to impose (Lemma 10).

644 Define general circuits over the basis  $\mathcal{B} = \{\wedge, \vee, \neg, 0, 1\}$  of Boolean functions: binary

645  $\wedge$  and  $\vee$ , unary  $\neg$  and zero-ary (constants) 1 and 0. Circuits take zero-ary variables in

646  $X = \{x_1, x_2, \dots, x_n\}$  and  $Y = \{y_1, y_2, \dots, y_m\}$  for some fixed  $n$  and  $m$  as inputs. Throughout

647 this work, we use the standard formulation of circuits consisting of single-sink and multi-

648 source DAGs where internal nodes, called gates, are labeled by function symbols, sources

649 are labeled by input variables, and edges as “wires” between the gates. We write  $V_C$  and

650  $E_C$  to denote the set of nodes and the set of edges of a circuit  $C$  respectively, omitting

651 the subscript when it is clear which circuit is being referenced. Circuits compute Boolean

652 functions through *substitution* followed by *evaluation*.

653 An *assignment*  $\rho$  of input variables is a mapping from the set of inputs to  $\{0, 1\}$ . To

654 substitute into a circuit according to an assignment  $\rho$ , each input  $x_i$  is replaced by the

655 constant  $\rho(x_i)$ . For a circuit  $G$  and assignment  $\rho$  we write  $G \upharpoonright \rho$  to denote the circuit obtained

656 by substituting into  $G$  according to  $\rho$ . To evaluate a circuit, the values of interior nodes

657 labeled by function symbols are computed in increasing topological order. Each gate’s value

658 is obtained by applying its function to the value of the node’s incoming wires. The output

659 of the circuit overall is the value of its sink.

660 Let  $\mathcal{F}_n$  be the family of Boolean functions on  $n$  variables. We say a circuit  $G$  on  $n$

661 variables computes  $g \in \mathcal{F}_n$  if for all  $\alpha \in \{0, 1\}^n$ ,  $G(\alpha) = g(\alpha)$ . The size of a circuit  $G$  is

662 denoted  $|G|$  and  $CC(g)$ , the circuit complexity of a Boolean function  $g$ , is the minimum size

663 of any circuit computing  $g$ . We study two notions of circuit size,  $\mu_D$  and  $\mu_R$ , which count the

664 number of binary gates and the total number of gates respectively. We decorate any notation

665 with  $\mathcal{D}$  or  $\mathcal{R}$  (e.g.  $CC(G)^{\mathcal{D}}$ ) to denote  $\mu_D$  and  $\mu_R$  whenever necessary, but will omit if the

666 measure is clear from context or if a statement holds for both measures. We say a circuit  $G$

667 computing  $g$  is optimal if  $|G| = CC(g)$  and, in  $\mathcal{D}$ , require that the circuit is *normalized*, i.e.

668 does not contain double-negations and every non- $\neg$  node feeds at most one  $\neg$  gate.

669 We will often order the nodes of a circuit by *depth*, the maximum number of binary gates

670 on any path from the node to the output. We sort a circuit’s nodes in *decreasing* order by

671 depth, i.e.  $\text{depth}(u) > \text{depth}(v)$  implies  $u$  appears before  $v$  in our ordering, breaking ties

672 arbitrarily. Such orderings are efficiently realizable as depth is efficiently computable. To

673 ensure we correctly account just binary gates for the depth, we first assign the outgoing

674 edges of each binary gate and negation gate with weight  $-1$  and  $0$  respectively. Then, we

675 simply take the circuit’s underlying DAG, reverse its edges, and compute the shortest path

676 from the output node to every other node in linear time [7].

677 We will sometimes work closely with specific parts of circuits. To this end we formally

678 define a subcircuit rooted at a vertex  $\alpha$ .

679 **► Definition 7 (Induced Subcircuit rooted at  $\alpha$ ).** Let  $C = (V, E)$  be a circuit and let  $\alpha \in V$ .

680 Let  $P_\alpha = \{b \in V \mid \exists \text{ a path from } \beta \text{ to } \alpha\}$ . The induced subcircuit rooted at  $\alpha$  in  $C$ , denoted

681  $C[\alpha]$ , is the vertex-induced subgraph of  $C$  whose vertex set is  $P_\alpha$  and whose edge set consists

682 of the edges in  $E_C$  whose endpoints are nodes in  $P_\alpha$ .

■ **Table 3** Gate elimination rules, categorized by their impact on fanout

| Fixing                          | Passing                              | Resolving                                | Pruning                                   |

|---------------------------------|--------------------------------------|------------------------------------------|-------------------------------------------|

| $0 \wedge \gamma \rightarrow 0$ | $1 \wedge \gamma \rightarrow \gamma$ | $\gamma \wedge \neg\gamma \rightarrow 0$ | $\gamma \wedge \gamma \rightarrow \gamma$ |

| $\gamma \wedge 0 \rightarrow 0$ | $\gamma \wedge 1 \rightarrow \gamma$ | $\neg\gamma \wedge \gamma \rightarrow 0$ |                                           |

| $1 \vee \gamma \rightarrow 1$   | $0 \vee \gamma \rightarrow \gamma$   | $\gamma \vee \neg\gamma \rightarrow 1$   | $\gamma \vee \gamma \rightarrow \gamma$   |

| $\gamma \vee 1 \rightarrow 1$   | $\gamma \vee 0 \rightarrow \gamma$   | $\neg\gamma \vee \gamma \rightarrow 1$   |                                           |

| $\neg 0 \rightarrow 1$          |                                      |                                          | $\neg\neg\gamma \rightarrow \gamma$       |

| $\neg 1 \rightarrow 0$          |                                      |                                          |                                           |

683

## B Gate Elimination

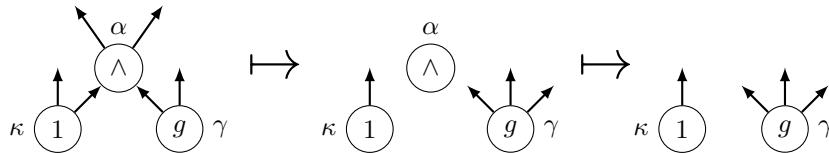

684 Most of the proofs in this paper involve arguments by gate elimination: we take a circuit,

685 substitute a subset of inputs with constants, and then eliminate gates according to a set of

686 basic simplification rules. This is illustrated in Figure 4.

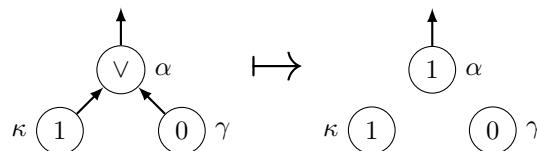

■ **Figure 4** An example of applying the passing simplification  $1 \wedge \gamma \rightarrow \gamma$ . Notice that  $\gamma$  inherits the fanout from  $\alpha$ , and  $\alpha$  can then be garbage collected.

687 Towards algorithms for the *f*-Simple Extension Problem, we fix a concrete encoding of

688 these circuit-manipulation steps. Gates  $\gamma$  are identified by natural numbers. We have one

689 book-keeping manipulation: *garbage collection* deletes a gate  $\gamma$  with no outgoing wires; i.e,

690  $\text{fanout}(\gamma) = 0$ . A garbage collection step is encoded by  $\langle \text{Gc}, \gamma \in \mathbb{N} \rangle$ .

691 The main *gate elimination* rules are organized into four categories in Table 3, according

692 to how they impact fanout. All these rules (i) eliminate at least one logic gate and (ii) have

693 no effect on the function computed by a circuit  $C$ , because they are Boolean identities.

694 A gate elimination step is encoded by the tuple  $\langle \text{GE}, r \in 17, b : \mathbb{N} \rightarrow 7 \rangle$  where  $r$  identifies

695 a rule and  $b$  is a “binding” that maps gates of  $C$  to gates of the circuit *pattern* on the left

696 hand side of rule  $r$ . Each pattern is a well-formed Boolean formula and thus has a *main*

697 *connective*  $\alpha$  in the standard sense. To apply a rule, examine the right hand side: if it is

698 ■ **a constant**  $c \in \{0, 1\}$ : delete all incoming wires to  $\alpha$  and change the type of  $\alpha$  to  $c$ .

699 ■ **a matched node (i.e.,  $\gamma$ )**: redirect all wires reading  $\alpha$  to read from  $\gamma$  instead.

700 Note that the identifier of  $\alpha$  **never** changes; only its type and incident wires. Depending

701 on the initial fanout of each gate involved in the pattern, applying a rule could totally

702 disconnect some gate(s) and leave the circuit in a state that needs garbage collection. We

703 introduce notation for applying sequences of these steps to circuits, and define composed

704 circuit manipulations that are “well behaved” with respect to specific circuits.

705 ► **Definition 8.** A simplification is a sequence of gate elimination and garbage collection

706 steps. If  $\lambda$  is a simplification and  $C$  is a circuit, write  $\lambda(C)$  to denote the new circuit obtained

707 by applying each step of  $\lambda$  to  $C$  in order. If a single step of  $\lambda$  fails to apply in  $C$ , then fix

708  $\lambda(C) = C$  so that invalid  $\lambda$  for  $C$  are idempotent by convention. A simplification  $\lambda$  is called

■ **Table 4** Changes to fanout after each type of gate elimination step.

| Fixing                                       | Passing                                                          | Resolving                                    | Pruning                                                             |

|----------------------------------------------|------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------|

| $\text{fo}'(\kappa) = \text{fo}(\kappa) - 1$ | $\text{fo}'(\kappa) = \text{fo}(\kappa) - 1$                     | $\text{fo}'(\alpha') = \text{fo}(\alpha)$    | $\text{fo}'(\gamma) \geq \text{fo}(\gamma) + \text{fo}(\alpha) - 2$ |

| $\text{fo}'(\gamma) = \text{fo}(\gamma) - 1$ | $\text{fo}'(\gamma) = \text{fo}(\gamma) + \text{fo}(\alpha) - 1$ | $\text{fo}'(\gamma) = \text{fo}(\gamma) - 1$ | $\text{fo}'(\alpha) = 0$                                            |

| $\text{fo}'(\alpha) = \text{fo}(\alpha)$     | $\text{fo}'(\alpha) = 0$                                         | $\text{fo}'(\neg) = \text{fo}(\neg) - 1$     | $\text{fo}'(\neg) = \text{fo}(\neg) - 1$                            |

- 709 ■ terminal for  $C$  if, for every  $\lambda'$  that extends  $\lambda$  by one additional gate elimination or garbage

710 collection step,  $\lambda(C) = \lambda'(C)$ , and/or

711 ■ layered for  $C$  if the depth of **binary** gates binding to  $\alpha$  in each step is non-decreasing.

712 Simplifications formalize every sequence of circuit-manipulation steps except for sub-

713 stitution. They change the function computed by a circuit if and only if some input gate

714 is garbage-collected. Simplifications suffice to impose convenient structural properties on

715 arbitrary circuits.

- 716 ▶ **Definition 9.** A circuit  $C$  is normalized or in normal form if

717 1.  $C$  is constant-free or  $C$  is a single constant,

718 2. every gate in  $C$  has a path to the output, and

719 3. no sub-circuit of  $C$  matches the left hand side of a gate elimination rule.

720 Any terminal simplification suffices to put a circuit  $C$  in normal form, and it straight-

721 forward to see that the number of constants in  $C$  lower-bounds the number of eliminated

722 gates. We require more: every circuit  $C$  can be normalized by a layered simplification, and

723 the number of eliminated gates is lower-bounded by the cumulative fanout of constants in  $C$ .

724 ▶ **Lemma 10.** For any well-formed circuit  $C$  with  $q$  constants that have total fanout  $\ell$ , there is

725 a terminal and layered simplification  $\lambda$  such that  $\lambda(C)$  is a single constant or  $|\lambda(C)| \leq |C| - \ell$ .

726 **Proof.** We update two potential functions as  $C$  is simplified:  $\phi_t$ , the cumulative fanout of

727 constants in  $C$  and  $\mu_t$ , the number of binary gates eliminated after  $t$  manipulations. Since

728 a circuit is normalized only when it is a single constant or  $\phi_t = 0$ , it suffices to exhibit a

729 terminal layered simplification  $\lambda$  such that  $\mu_t \geq \ell$  if  $\phi_t = 0$ .

730 Sort the gates of  $C$  by depth (breaking ties arbitrarily) to fix a total order on gates.

731 This ordering remains consistent throughout the entirety of simplification. Constructing  $\lambda$  is